#### Chapter

# Overview of Selected Issues Related to Soldering

Karel Dušek, David Bušek and Petr Veselý

#### Abstract

The formation of defects and imperfections in the soldering process can have many causes, which primarily include a poorly setup technological process, inappropriate or inappropriately used materials and their combinations, the effect of the surroundings and design errors. This chapter lists some examples of errors that can occur in soldering, while review is devoted to selected defects: non-wettability of the solder pads, dewetting, wrong solder mask design, warpage, head-in-pillow, cracks in the joints, pad cratering, black pad, solder beading, tombstoning, dendrites, voids, flux spattering from the solder paste, popcorning and whiskers.

**Keywords:** electronic assembly, soldering, reflow soldering, soldering defects, reliability issues

#### 1. Introduction

A significant change in soldering technology was the transition to lead-free soldering. With this change and the increasing miniaturisation of electrical equipment comes the associated issue of developing suitable alloys, production technology, etc. Over time, soldering has become a very complex process, with many factors affecting the final quality of the solder joints, and thus the product.

The formation of defects and imperfections in the soldering process can have many causes, which primarily include a poorly setup technological process, inappropriate or inappropriately used materials and their combinations, the effect of the surroundings and design errors. This chapter lists some examples of errors that can occur in soldering.

#### 2. Non-wettability

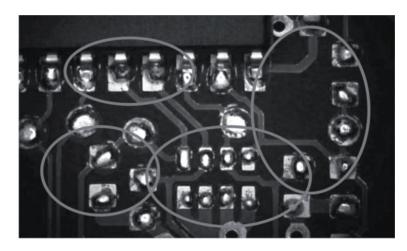

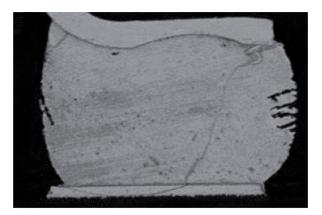

One of the problems is the non-wettability of the soldering pads. During the soldering process, the soldering pads are not sufficiently wetted with the solder alloy (the solder does not create a connection with the entire surface of the soldered area). An example of this defect is shown in **Figure 1**.

This defect may be caused by the soldering pads being too oxidised, the flux not being active enough, insufficient PCB warming, soldering pad contamination as well as, for instance, a poor solder mask coating [1].

Figure 1. Problems with the non-wettability of soldering pads.

## 3. Dewetting

Dewetting usually happens in the case of a prolonged heating, leading to the formation of an intermetallic that results in a change in the composition of the solder alloy as is the case, for example, when soldering a tin-lead solder on copper substrate, where the tin is sucked out of the solder alloy, which is involved in the formation of an intermetallic layer, thus increasing the proportion of lead in the solder alloy, which has poor wetting. Dewetting may also arise due to the dissolution of the precious metals in the solder alloy or the influence of a poor soldering surface under the surface finish. Photos of dewetted surfaces are shown in **Figure 2**.

Figure 2. Photos of soldering pads dewetting.

## 4. Wrong solder mask design

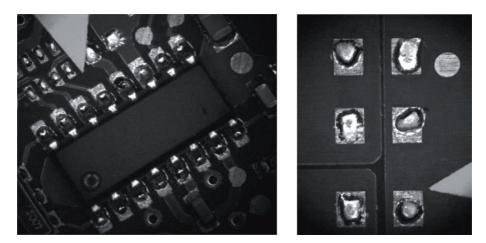

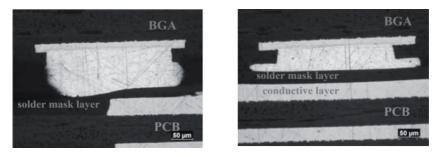

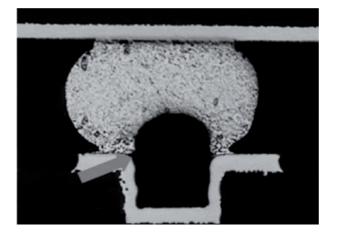

Another problem that can occur with the solder mask is due to wrong PCB design, especially if the solder mask is used to cover pads for unused BGA package leads (see **Figures 3** and 4). In this case the BGA balls become deformed and the risk of bridging is increased.

Figure 3.

Section—deformation of BGA balls due to inappropriate solder mask design.

Figure 4.

Detail of the sections from **Figure 3**, showing the deformation of BGA balls due to inappropriate solder mask design.

This is mainly caused by the designer's unfamiliarity with correct PCB design. A soldering pad on the PCB must be present for each BGA terminal, even if the terminal is not used.

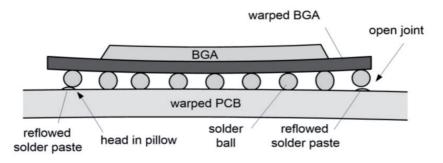

#### 5. Warpage effect: head-in-pillow effect

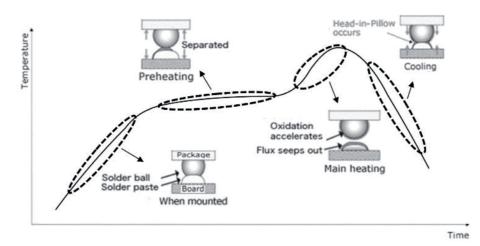

In the case of differing thermal expansion, coefficients between the PCB and the component package, during heating/cooling, there is mutual deflection/ deformation called the "warpage effect". This effect may result in correctable errors (bridges, open joints), but also in unrepairable errors—cracks (on components, inside the PCB) [2]. This effect, along with some other defects, including the "Head-in-Pillow" effect, is shown in **Figure 5**.

The Head-in-Pillow effect is a characteristic in the case of soldering of BGA components. During heating the BGA terminal/balls lift up from the soldering pad coated with solder paste. In the reflow zone, the soldering paste and the BGA solder alloy balls reflow independently. During cooling this sag is counteracted, nevertheless

Figure 5.

Schematic representation of the warpage effect.

Figure 6. Head-in-pillow effect in connection with the temperature profile.

Figure 7. Photo of a microsection of the head-in-pillow effect.

the reflowed solder alloy on the solder pad no longer joins with the reflowed BGA solder alloy ball. The Head-in-Pillow effect in connection with the temperature profile is shown in **Figure 6**, together with a photo of a microsection in **Figure 7**.

## 6. Cracks: pad cratering

Cracks occur not only in the soldered joints, but also in the components and PCB. Due to mechanical, thermal and combined stress, the material is under tension, which results in cracks forming in the weakest spot, together with a release of the tension [3].

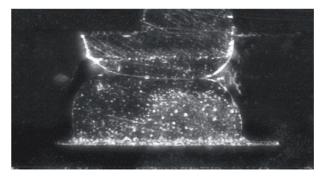

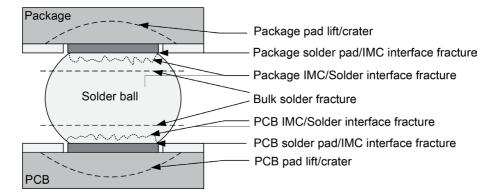

The location of the cracks depends on many factors (the materials used, the type of soldering technology, the package, the PCB material, geometric factors, etc.) [4, 5]. **Figure 8** shows an overview of crack failures occurring in a PCB assembly.

An example of a crack in the site of the intermetallic alloy on the interface between the BGA package's terminal and the ball of solder alloy is shown in the microsection in **Figure 9**. Due to their minimum dimensions, these errors are difficult to detect using X-ray inspection.

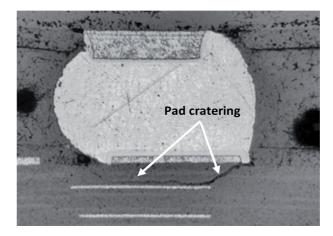

Another example of a crack is pad cratering where a crack is formed within the PCB under the soldering pad (see **Figure 10**). This defect does not manifest during a functional electrical test, and it is not even possible to detect it with the non-destructive methods for the output check.

Figure 8. Overview of crack failures occurring in a PCB assembly.

#### Figure 9.

A longitudinal crack between the solder joint and the BGA package's terminal.

Figure 10. Microsection of a BGA terminal soldered to a PCB with a pad cratering defect.

A pad cratering defect can be compounded by the use of lead-free solder alloys, where the higher temperatures used for lead-free solder alloys cause greater tension in the materials used [6, 7]. In addition, the lead-free solder alloys are significantly stiffer than tin-lead eutectic solder alloys; therefore, they transfer greater stress under the package pads during a mechanical stress [8].

Static or cyclic mechanical stress or thermal cycling can lead to the cracks spreading and the consequent failure of the device [9]. Stress can affect a mounted PCB even without external influences; this is called residual stress (tension that remains in the material even though the cause of stress has been removed). The source of the residual stress is primarily the manufacturing process in which many stress factors affect the components [10]. This primarily concerns the soldering process, where the elevated temperature leads to the fixation of components that often have different coefficients of thermal expansion.

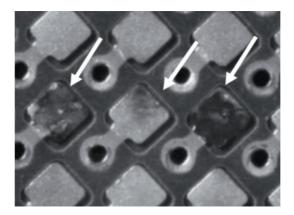

#### 7. Black pad effect

The black pad effect is a characteristic for Ni/Au surface finishes, where Ni contains higher amount of phosphor. During the Ni/Au surface layer creation, the nickel layer is covered with a thin layer of gold; this plating process may lead to corrosion of the nickel surface. The final Au coating can provide good wetting for the solder alloy, even though it has an oxidised Ni-P layer under it. Another cause of the black pad effect is the solder pads reacting with a lead-free alloy with a higher tin content at a higher temperature (longer reaction time). This reaction produces a thicker layer (rich in phosphorus) on the interface, which has a defective structure (microfractures, microvoids). Due to the black pad effect, the soldered joint is considerably weakened mechanically and ultimately will break the conductive connection between the component's terminal and the soldering pad. This fault is very difficult to detect; thus it may occur on devices that have passed output control tests and have already been sent to market (**Figure 11**).

**Figure 11.** *Photo of black pad effect after stripping off the immersion gold layer.*

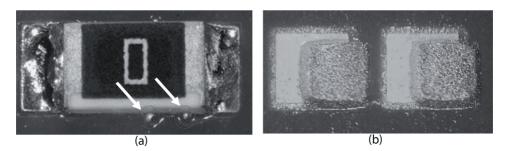

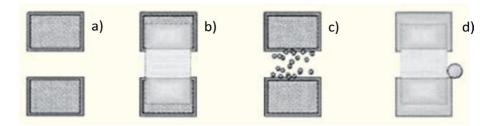

#### 8. Solder beading

The presence of balls of solder alloy next to the package (solder beading) is an error that is easily detectable by optical inspection methods. An example of balls next to the component package is shown in **Figure 12a**. The device's reliability is compromised in the event that the conductive ball becomes free, which can be a potential risk of a fault in the device, for example, it can cause an accidental short circuit. The occurrence of the balls is due to inaccurate deposition of solder paste (either due to solder paste misprint or due to excessive amount of the deposited paste), where particles of the solder alloy get under the package when attaching the component [11]. An example of inaccurate application of solder paste is shown in

#### Figure 12.

(a) Solder alloy balls occurring next to the component's package. (b) Inaccurate deposition of solder paste with regard to the solder pads.

#### Figure 13.

Schematic representation of the principle of balls forming next to the component's package: (a) solder paste deposited on solder pads (b) mounting the component (c) during reflow particles of solder paste partially agglomerate (d) a ball forms next to the component's package.

**Figure 12b**. The solder alloy particles partially agglomerate under the component package during reflow, and the component's package squeezes them out of its side. This phenomenon is illustrated schematically in **Figure 13**. If the error occurs regularly during mass production for a specific group of components, it is necessary to modify the dimensions of apertures in the stencil.

#### 9. Tombstone effect

The tombstone effect (or Manhattan effect, drawbridging or the Grabstein effect) is a phenomenon which is characterised by one of the sides of a small SMD component (typically in a 0805, 0603, 0402 and 0201 package) lifting up during reflow. A photo of the tombstone effect is shown in **Figure 14**.

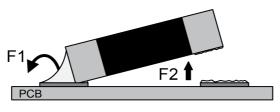

Tombstone effect is caused by an imbalance of wetting forces during the reflow process [12]. This can be caused by unequal amount of solder paste applied to the connecting pads, differently sized soldering pads, eccentrically mounted component, different wettability of soldering pads, a different time of solder melting on each side of the component, etc. or by upward push by solvent vapours from flux during an asymmetric reflow process [13]. The effect of the wetting force, or upward push force from solvent vapours, is depicted in **Figure 15**.

The frequency of the tombstone effect is also influenced by the reflow technology used. The feedback from industrial practice says that this effect is more frequent in vapour-phase soldering technology. This has been experimentally verified and presented in the publication dealing with tombstone effect [14, 15]. Currently work is being done on a more detailed explanation of the cause of the higher occurrence of the tombstone effect in vapour-phase soldering.

**Figure 14.** *Photo of the tombstone effect.*

**Figure 15.** Schematic representation of the wetting force (F1); upward push force from solvent vapours (F2).

## 10. Dendrites

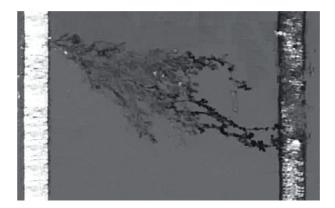

Dendrites grow due to electrochemical migration when metal ions go into the electrolytic solution at the anode, plating out at the cathode and creating needle- or treelike formations on the PCB substrate (see photos in **Figure 16**) [16]. Electrochemical migration can be defined as the movement of a metal ion in an electrolytic solution between two neighbouring conductors with different electrical potential.

The time required to create dendritic bridges, which cause short circuits between two conductive paths, is determined by several factors including relative humidity,

**Figure 16.** *Photo of dendrite.*

temperature, conductor material, conductor spacing, voltage difference, contamination amount, contamination type, etc. [17–19].

The growth of dendrites has become a more serious issue, mainly due to the constant miniaturisation of electronic components (decreasing distance between the cathode and the anode) and the use of newer fluxes (especially no-clean fluxes). Manufacturers use no-clean fluxes to remove the washing process from production and reduce production costs. Despite this, these fluxes, under certain conditions (high humidity, significant temperature changes), are a good basis for creating an electrolytic solution. To prevent the growth of dendrites, it is necessary to thoroughly wash (even no-clean fluxes were used) the PCB after soldering.

#### 11. Voids

Voids are non-conductive cavities within the soldered joint, and their excessive presence poses a significant reliability risk for the manufactured product, especially in power electronics, where higher currents are present [20]. Voids are formed during the soldering process, their presence in the soldered joint causes the displacement of electrical and thermal paths, the resistance is higher and the temperature stress is non-uniform. This subsequently causes cracks and lowers the mechanical shock tolerance of the whole PCB.

With the advent of lead-free soldering (new material base, different temperature profiles, different types of fluxes, higher surface tension of solder, etc.), a higher incidence of voids was detected, leading to the lower reliability of soldered joints. Increased attention is therefore paid to the voiding issue.

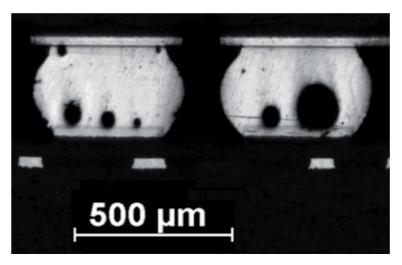

Voids can be classified into several categories [21]. There are macro- and microvoids, shrinkage voids, voids in microvias, Kirkendall voids and pinhole voids (see **Figure 17**).

#### 11.1 Macrovoids

Macrovoids are the most commonly occurring type of voids. Macrovoids are formed by the evaporation of gases from fluxes and soldering pastes during the reflow process. Macrovoids may occur anywhere in the solder joint, and their diameter is around  $100-300 \mu m$ .

The factors that affect the size of the macrovoids are the solder paste's properties (particle size, composition, melting temperature and oxide content), flux (viscosity,

#### Figure 17.

Soldered joint and the location of different types of voids. Intermetallic layer contains Kirkendall voids; pinholes are located on the boundary between the intermetallic layer and the PCB.

surface tension, activator, solvent, etc.), components (geometry, shape, terminal oxidation, etc.) and the process (thickness, the shape and the parameters of the solder paste's printed layer, temperature profile) [22–26]. An example of macrovoids in the solder joints of a soldered BGA package on the PCB is given in **Figure 18**.

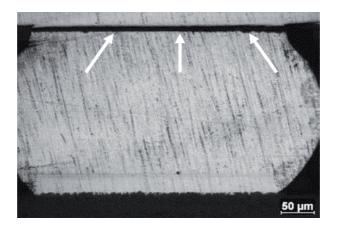

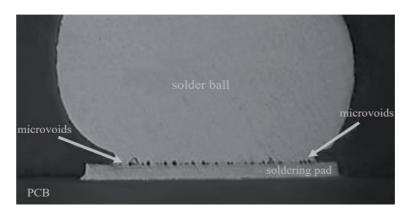

#### 11.2 Planar microvoids

Microvoids are characterised by their small diameter, less than 25  $\mu$ m. Their occurrence is typical for Ni/Au, OSP and Ag finishes [27]. There are planar (one plane) on the solder pad/solder alloy interface; due to this, the joint's mechanical strength is significantly reduced. The cause of these voids' formation is not yet fully clarified. An example of planar microvoids on the interface of the solder pad/solder alloy is shown in **Figure 19**.

#### 11.3 Shrinkage voids

Shrinkage voids are voids with rough tree-like, branching edges pointing from the joint's surface towards the solder joints' core. They are characteristics for SAC solder

Figure 18. Macrovoids within the BGA solder joints.

Figure 19. Planar microvoids.

alloys. The cause of these voids' formation is the solder solidification process, when the solder shrinks during slow cooling. Their occurrence can be avoided by controlled cooling. It has not yet been proven that these voids have a negative effect on the reliability of soldered joints. An example of shrinkage voids is shown in **Figure 20**.

#### 11.4 Microvia voids

This type of void arises from gases escaping from the microvia (plated holes with a diameter smaller or equal to 150  $\mu$ m, used for interconnection of conductive paths between the individual PCB layers) during the soldering process. The solder has inadequate wettability and is not able to penetrate inside a microvia. These voids can greatly affect the reliability of a solder joint; therefore, it is recommended to take them into account during design (**Figure 21**).

#### 11.5 Kirkendall (IMC) voids

Kirkendall voids arise in the intermetallic layer between the solder and the solder pad. They are created when joining two metals with different diffusion coefficients. These voids are most commonly located on the interface between a tin solder and

Figure 20. Shrinkage voids.

Figure 21. Microvia void.

a copper solder pad. Tin has a lower diffusion coefficient and thus penetrates more slowly into the copper than copper into tin.

#### 11.6 Pinhole voids

Pinhole voids arise when a gas leaks from metal soldering pads during the soldering process. These voids have very small dimensions, on average around 1–3 µm. Their appearance is due to substances absorbed by substrates from previous processes. They mostly occur in the case of galvanic copper surface finish.

#### 12. Flux spattering from the soldering paste

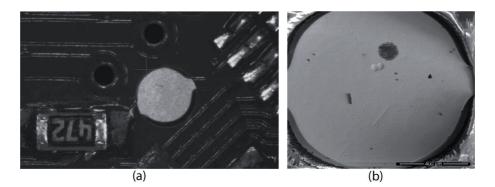

During the reflow process, the flux may spatter from the soldering paste. If the PCB is cleaned after soldering, flux spattering need not necessarily be considered a problem. If PCB cleaning is not included in the process, then flux residues can not only be the cause of future corrosion, but flux spatter can leave stains on the test surfaces intended for the subsequent electrical testing methods.

If a flux stain on the test surface gets into sites where the contact test tip is in contact with the test surface, then, due to the non-conducting nature of the flux, the electrical test evaluates the product as a reject, even if the product is fully functional. In addition, these stains are, in most cases, clear and therefore difficult to detect. An example of a photo of the test pads on a PCB is given in **Figure 22** along with an image from an electron microscope, where a dark stain is evident; the source of the stain was flux spattering.

There are various sources of non-conducting stains on the test surfaces, for example, the solder mask, organic coatings, inappropriate materials used when maintaining technological equipment, etc. Diagnosis of the cause can be very problematic.

Figure 22.

Test surfaces for electrical testing methods: (a) photo from an optical microscope and (b) photo from an electron microscope—a dark stain is obvious, and the source of the stain was flux spattering.

#### 13. Popcorn effect

During the soldering process, heating the mounted PCB, some components may experience absorbed moisture turning into steam, which may result in damage (delamination, cracking the component's package). The components absorb moisture during their manufacture and storage. It is therefore necessary to dry components that are sensitive to moisture absorption before they are mounted and

**Figure 23.** *Schematic representation of the popcorn effect.*

soldered. The popcorn effect is schematically shown in **Figure 23**. With the advent of lead-free soldering, this effect occurs more frequently due to the use of higher soldering temperatures. In some cases, when the package cracks from the PCB side, this defect is very difficult to detect.

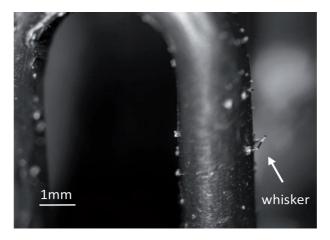

## 14. Whiskers

Whiskers are electrically conductive and relatively mechanically resistant crystals growing on the surface of some metals. They may grow on the surface of the solder alloys with a high tin content (majority of lead-free solder alloys). It most

Figure 24. Photos of whiskers.

often concerns surfaces where tin (mainly galvanic) was used as a final finish [28, 29]. Whiskers can be straight, curved or kinked. Photos of whiskers are given in **Figure 24**.

Whiskers represent a very serious threat to the proper function and reliability of electronic equipment, mainly from the perspective of creating a short circuit (permanent, short-term or possible arcing). Therefore, materials with the potential risk of the growth of whiskers are not used in those industrial sectors that have higher demands on reliability and where they could cause large-scale damage or pose a threat to human life.

Whisker diameters range from 1 to 10  $\mu$ m. Their length is typically in the order of micrometres, but in extreme cases they can reach lengths of up to 1 cm. The rate of whisker growth is determined by many factors; the literature [11] gives the approximate growth rate of whiskers in the range of 5 mm/year up to 1 cm/year. The following factors affect the whiskers' growth:

- Compressive stress

- External—caused by mechanical stress

- Internal—caused by the size of the grains inside the solder alloy, the type of surface finish of the solder pads, a different thermal expansion coefficient of the substrate and the solder and scratches on the surface

- The crystalline structure (grain shape and orientation) of the solder alloy and the presence of intermetallic compounds

- Temperature and humidity [30]

Due to their size and growth on shiny surfaces, whiskers are very difficult to detect by classical optical methods. The experimental results of whisker growth are unpredictable and unrepeatable, and so far the exact mechanism of their growth is not known.

## **Author details**

Karel Dušek<sup>\*</sup>, David Bušek and Petr Veselý Department of Electrotechnology, Faculty of Electrical Engineering, Czech Technical University in Prague, Prague, Czech Republic

\*Address all correspondence to: karel.dusek@fel.cvut.cz

#### IntechOpen

© 2020 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/ by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

#### References

[1] Dušek K, Plaček M, Bušek D, Dvořáková K, Rudajevová A. Study of influence of thermal capacity and flux activity on the solderability. In: Proceedings of the 2014 37th International Spring Seminar on Electronics Technology (ISSE), IEEE. 2014. pp. 185-188

[2] Bušek D, Dušek K, Plaček M, Urbánek J, Horník J, Holec J.

Determination of BGA solder joint detachment cause-warpage effect. In: 2015 38th International Spring Seminar on Electronics Technology (ISSE), IEEE.

2015. pp. 306-309

[3] Otáhal A, Adamek M, Jansa V, Szendiuch I. Investigation of the mechanical properties of lead-free solder materials. Key Engineering Materials. 2014;**592-593**:453-456. DOI: 10.4028/www.scientific.net/ KEM.592-593.453

[4] Dušek K, Bušek D, Beran T, Rudajevova A. Comparison of shear strength of soldered SMD resistors for various solder alloys. In: 2015

38th International Spring Seminar on Electronics Technology (ISSE), IEEE.

2015. pp. 237-240

[5] Garami T, Krammer O, Harsányi G, Martinek P. Method for validating CT length measurement of cracks inside solder joints. Soldering & Surface Mount Technology. 2016;**28**:13-17

[6] Long G, Embree T, Mukadam M, Parupalli S, Vasudevan V. Lead free assembly impacts on laminate material properties and pad crater failures. In: IPC APEX/EXPO Conference. 2007

[7] Dušek K, Rudajevová A. Influence of latent heat released from solder joints II: PCB deformation during reflow and pad cratering defects. Journal of Materials Science: Materials in Electronics. 2017;**28**:1070-1077

[8] Ma H. Effects of temperature and strain rate on the mechanical properties of lead-free solders. Journal of Materials Science. 2010;**45**:2351-2358

[9] Pietriková A, Durisin J, Ďurišin J. VPS and reliability of solder joint. In: 2009 15th International Symposium for Design and Technology of Electronics Packages (SIITME). 2009. pp. 395-398. DOI: 10.1109/SIITME.2009.5407338

[10] Rudajevova A, Dušek K. Residual strain in PCBs with Cu-plated holes. Journal of Electronic Materials. 2017;46:6984-6991

[11] Pietriková A, Ďurišin J, Mach P. Diagnostika a optimalizácia pou žitia ekologických materiálov pre vodivé spájanie v elektronike. 1. vydanie. Košice: Fakulta elektrotechniky a informatiky Technickej university v Košiciach; 2010

[12] Zero-defect printing shifts blame for poor-quality soldering. 31 July 2002. Zetech. Dataweek n.d. Available from: http://www.dataweek.co.za/news. aspx?pklnewsid=7525 [Accessed: 20 March 2016]

[13] How Reduce Tombstoning of Small Chip Components—Tombstoning explained.pdf n.d. Available from: http://metallicresources.com/ documents/Tombstoning%20explained. pdf [Accessed: 20 March 2016]

[14] Dusek K, Straka V, Brejcha M,

Beshajova Pelikanova I. Influence of type of reflow technology and type of surface finish on tomb stone effect. In: 2013 36th International Spring Seminar on Electronics Technology (ISSE), IEEE.

2013. pp. 132-135

[15] Dušek K, Bušek D, Plaček M, Géczy A, Krammer O, Illés B. Influence of vapor phase soldering fluid Galden on wetting forces (tombstone effect). Journal of Materials Processing Technology. 2018;**251**:20-25

[16] Ready WJ, Turbini LJ. The effect of flux chemistry, applied voltage, conductor spacing, and temperature on conductive anodic filament formation. Journal of Electronic Materials. 2002;**31**:1208-1224

[17] Bumiller E, Hillman C. A review of models for time-to-failure due to metallic migration mechanisms. In: White Paper. DfR Solutions; 2006

[18] Steiner F, Hirman M, Rendl K,

Wirth V. Optimization of soldering process to reduce contamination and related consequences. In: 2018

41st International Spring Seminar on Electronics Technology (ISSE).

2018. pp. 1-6. DOI: 10.1109/

ISSE.2018.8443691

[19] Medgyes B, Horváth B, Illés B, Shinohara T, Tahara A, Harsányi G, et al. Microstructure and elemental composition of electrochemically formed dendrites on lead-free microalloyed low Ag solder alloys used in electronics. Corrosion Science. 2015;**92**:43-47. DOI: 10.1016/j. corsci.2014.11.004

[20] Diehm R, Nowottnick M, Pape U. Reduction of voids in solder joints an alternative to vacuum soldering. In: Proceedings of the IPC APEX EXPO. San Diego, CA; Vol. 28. 2012. p. 8

[21] Aspandiar Raiyo F. Voids in solder joints. Journal of SMT Article. 2006;**19-4**:406-415

[22] Primavera AA, Sturm R,Prasad S, Srihari K. Factors that affect void formation in BGA assembly.Journal of Surface Mount Technology.1999;12:19-26

[23] Bušek D, Dušek K, Rŭžička D, Plaček M, Mach P, Urbánek J, et al. Flux effect on void quantity and size in soldered joints. Microelectronics Reliability. 2016;**60**:135-140

[24] Steiner F, Wirth V, Hirman M. Relationship of soldering profile, voids formation and strength of soldered joints. 2019 42nd International Spring Seminar on Electronics Technology (ISSE). 2019:1-6. DOI: 10.1109/ ISSE.2019.8810303

[25] Hirman M, Steiner F. Optimization of solder paste quantity considering the properties of solder joints. Soldering & Surface Mount Technology.2017;29:15-22

[26] Skácel J, Otáhal A, Szendiuch I.

Influence of electric current at solidification of solder. In: 2019 42nd International Spring Seminar on Electronics Technology (ISSE). 2019.

pp. 1-5. DOI: 10.1109/ISSE.2019.8810308

[27] Aspandiar R. Planar microvoids. In: Intel Lead Free Symposium, Scottsdale, AZ. 2006

[28] Bušek D, Vávra J, Dušek K. Whisker growth and its dependence on substrate type and applied stress. In: 2016 39th International Spring Seminar on Electronics Technology, IEEE. 2016. pp. 263-266

[29] Horváth B, Illés B, Shinohara T, Harsányi G. Whisker growth on annealed and recrystallized tin platings. Thin Solid Films. 2012;**520**:5733-5740

[30] Illés B, Horváth B, Géczy A, Krammer O, Dušek K. Corrosioninduced tin whisker growth in electronic devices: A review. Soldering & Surface Mount Technology. 2017;**29**:59-68. DOI: 10.1108/SSMT-10-2016-0023